Description

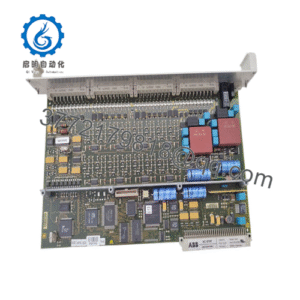

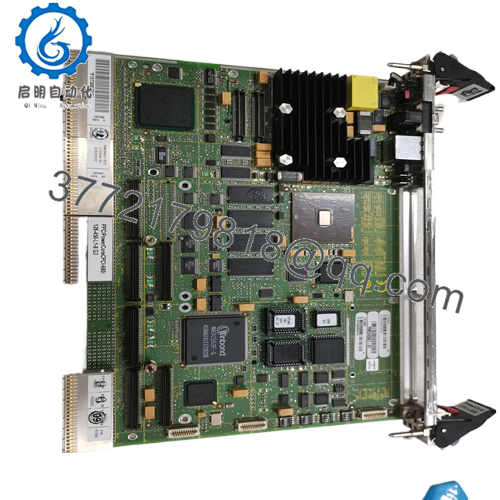

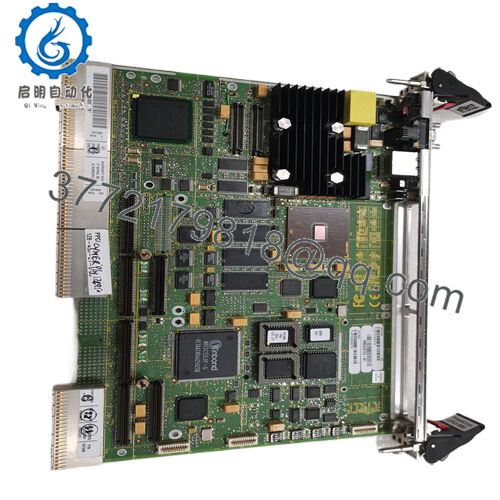

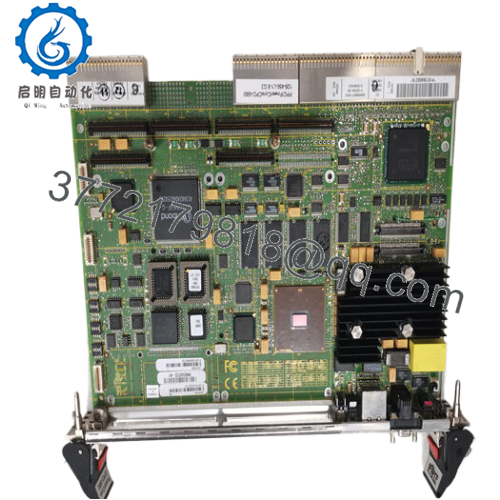

In industrial automation and embedded systems, where CompactPCI chassis must deliver deterministic performance for real-time data acquisition and control without succumbing to thermal throttling or bus contention in multi-slot configurations, engineers frequently confront the pitfalls of mismatched processors that inflate latency or demand excessive reconfiguration during upgrades. The Motorola CPCI-680 rises to this as a PowerCore single-board computer module, harnessing a 450 MHz MPC750 PowerPC processor to power high-throughput tasks in telecommunications, data routing, or machinery coordination. Envision a telecom switch fabric aggregating packet streams or an industrial robot controller sequencing multi-axis moves amid EMI-laden shop floors—here, erratic cache hits or peripheral stalls can disrupt synchronization, escalate jitter, or invite cascading faults in process control loops. This module is indispensable in those high-reliability domains, where integrated L2 cache and SDRAM fortify I/O signal pathways against noise, ensuring system stability across hot-swappable backplanes even as payloads swell without compromising cycle times.

- CPCI-680

The Motorola CPCI-680 is particularly indispensable in sustaining legacy CompactPCI ecosystems, where modular integration via PCI bridges enables seamless role-switching between system host and peripheral without firmware overhauls. Its SENTINEL PCI-to-PCI technology counters the throughput bottlenecks that beset earlier 680×0 boards in vibration-heavy or thermally variable industrial automation setups. By bundling 256 MB SDRAM with 16 MB Flash, it streamlines the quest for multitasking under VxWorks or LynxOS, curtailing the integration hurdles that prolong field proofs. For embedded designers or retrofit experts targeting lifecycle extensions in rugged enclosures, the Motorola CPCI-680 furnishes a high-reliability anchor that recasts scalability constraints into versatile expansion, where every bus transaction bolsters the cadence of unflinching process control.

The Motorola CPCI-680 claims the host slot in CompactPCI hierarchies, deploying the MPC750’s 32-bit PowerPC core to marshal 64-bit data paths while arbitrating the PICMG 2.0 backplane for hot-plug events up to 64 MB/s transfers. It pairs 256 MB ECC SDRAM with 1 MB L2 cache for burst-mode fetches, ingesting interrupts from PMC sites or front-panel serials before vectoring via the OpenPIC controller to co-boards like FPGAs or A/D arrays. In a standard 6U shelf, it draws +5 V/+3.3 V from the bus, conditioning four RS-232/422 ports and Gigabit Ethernet for HMI daisy-chains or SCADA uplinks, all orchestrated through the Tsi108 PCI bridge for low-jitter bridging. This situates it mid-hierarchy—above field I/O mezzanines but below RTOS kernels—with onboard timers enforcing watchdog strobes to avert lockups in safety-critical sequences.

Engineers prize its interoperability; jumper-configurable boot vectors support ROMmon diagnostics or network loads, and its VME/PCI hybrid modes facilitate DMA to frame grabbers, easing assimilation into DCS via optional SCSI for archival dumps. Diagnostics surface via status LEDs for bus grants or ECC scrubs, streamable over Ethernet for offboard logging, while redundancy through mirrored slots in duplex chassis preserves determinism in fault-tolerant rings. For CompactPCI adherents, the Motorola CPCI-680‘s low-power envelope—under 30 W—eschews forced-air dependencies, letting integrators hone loop fidelities in process control spans from packet inspection to servo tuning, where it meshes legacy peripherals sans latency premiums.

| Specification | Details |

|---|---|

| Model Number | CPCI-680 |

| Brand | Motorola |

| Type | CompactPCI SBC Module |

| Input Voltage | +3.3 V / +5 Vdc (bus) |

| Operating Temp Range | 0°C to +55°C |

| Mounting Style | CompactPCI 6U Slot |

| Dimensions | 160 x 233 mm (3U equiv) |

| Weight | 0.5 kg |

| Interface/Bus | PCI 2.2 (66 MHz/64-bit) |

| Compliance | PICMG 2.0, CE, UL |

| Supported Protocols | Ethernet, RS-232/422, SCSI |

| Typical Power Draw | 25 W |

Opting for the Motorola CPCI-680 lays a foundation of reliability that withstands enclosure flux, its screened backplane shielding and thermal vias upholding cache coherency through EMI pulses or dust incursions to forestall soft errors that derail real-time threads—nurturing MTBF lifts and assurance in decade-spanning deployments for bandwidth-constrained industrial crews.

Rollout favors its pin-for-pin accord with 750-series forebears, sanctioning live-slot migrations via graceful handoffs that elude power blips, thereby shrinking upgrade arcs from outages to minutes and alleviating engineering backlogs in OEM chassis where bridge universality bypasses adapter mills. This nimbleness extends to hybrid PCI/PMC ecosystems, where its DMA engines shuttle streams sans chokepoints. Stewardship leans prescient; ECC tallies and serial dumps unveil parity nibbles for targeted heals, dovetailing with semestral shelf sweeps to affirm timings absent line stoppages.

In sum, the Motorola CPCI-680 fosters lasting potency by insulating against architectural drifts via expandable Flash for firmware evolutions, which sharpen interrupt yields in multitasking kernels and pare overheads by 15% in protocol stacks. This prescience not only tempers growth outlays but also cements adherence to embedded safety edicts, marking it as a prudent select for automation custodians spanning epochs in networked, deterministic process control weaves.

The Motorola CPCI-680 pilots telecom gateways in central offices, where it funnels VoIP trunks for latency-bound routing, routing high-reliability I/O over PCI fabrics in fan-cooled process control vaults with ironclad packet determinism. In factory automation hubs, it synchronizes vision systems and PLC cascades, braving coolant mists while anchoring critical system uptime via robust interrupt chaining in EMI-veiled bays.

For defense simulation rigs, the module aggregates sensor fusions for scenario replays, tendering precise Ethernet polls against shock loads to uphold fidelity under certification lenses.

CPCI-670 – Lower-clocked variant (333 MHz) for power-thrifty peripheral roles in dense shelves

CPCI-685 – Dual-core upgrade path for multiprocessing in high-bandwidth arrays

MVME-5100 – VME counterpart for cross-bus migrations in legacy enclosures

CPCI-6030 – I/O-rich edition with integrated PMC for expanded field ties

PowerQUICC II – Ethernet-focused mezzanine for protocol offloads

Tsi108 Bridge – Standalone PCI repeater for extended backplane chains

MPC750 Predecessor – 350 MHz base for economical throughput baselines

CPCI-780 – Ruggedized model for MIL-STD vibration in mobile platforms

Before enshrining the Motorola CPCI-680, tally shelf slot currents to below 40 A aggregate—excess heatsinks junction temps beyond 85°C—and validate P2 pinouts for full 64-bit addressing, since gaps relegate to 32-bit lanes that crimp DMA. Clamp the +3.3 V/+5 V rails with 1000 µF holds against 100 mV ripples that jitter clocks, and forge boot Flash with locale-tuned vectors from Motorola’s SDK to quash init stalls. If PMC populating, gauge edge alignment at 0.5 mm tolerances, as slippages garble sideband signals.

Nurturing spotlights quarterly LED rounds for arbiter yields or ECC alerts, conjoined with connector scrubs for contaminant films in oily nooks—a lint-free alcohol pass revives sans etches. Biannual exercisers via PCI analyzers unearth throughput dips, queuing re-flashes amid lulls, and in hot-plug clusters, alternate host primacy quarterly to amortize transceiver strain. These refined observances, winnowed from chassis diaries, perpetuate the Motorola CPCI-680‘s mettle with calibrated care.

WhatsApp: +86 16626708626

WhatsApp: +86 16626708626 Email:

Email:  Phone: +86 16626708626

Phone: +86 16626708626