Description

What This Product Solves

In the high-stakes theater of semiconductor manufacturing and process control, synchronizing the chaotic dance of robotic arms, wafer chucks, and gas delivery valves in plasma etch tools is a razor-edge imperative—especially in Lam Research platforms like the TCP 9400 or Kiyo series, where a mere 20ms desync in stepper commands can skew etch profiles by microns, spawning sidewall roughness or undercut defects that torpedo device performance and inflate scrap yields beyond 2% in fabs straining for 3nm gate-all-arounds under the unyielding glare of SEMI E10 downtime quotas and escalating cleanroom kilowatt costs. These synchronization stumbles intensify amid recipe ramps or multi-lot transitions, where EMI from 13.56 MHz coils or vibration from turbo pumps corrupts discrete signals, compelling teams to throttle velocities or layer in redundant checks that sap efficiency and swell engineering cycles in environments where every etch etch counts toward quarterly node conquests.

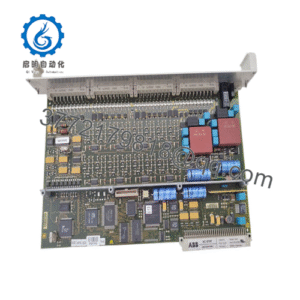

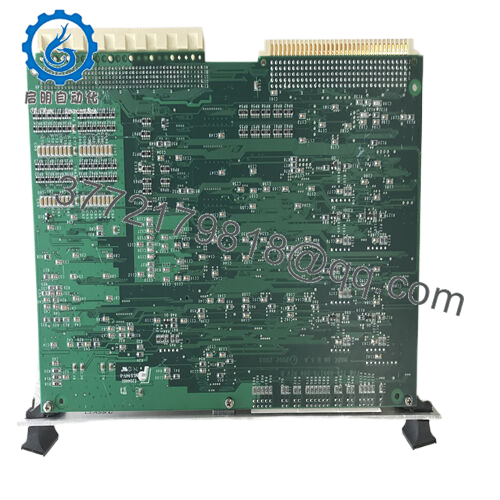

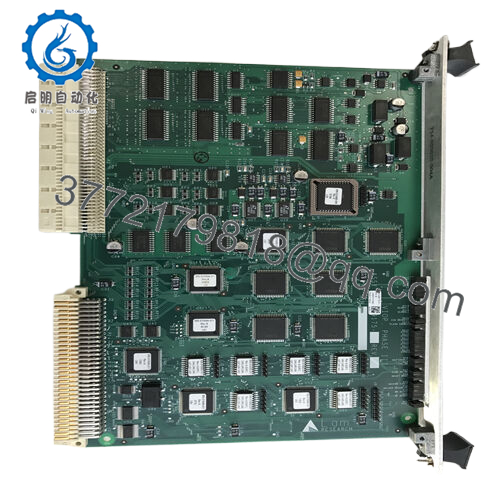

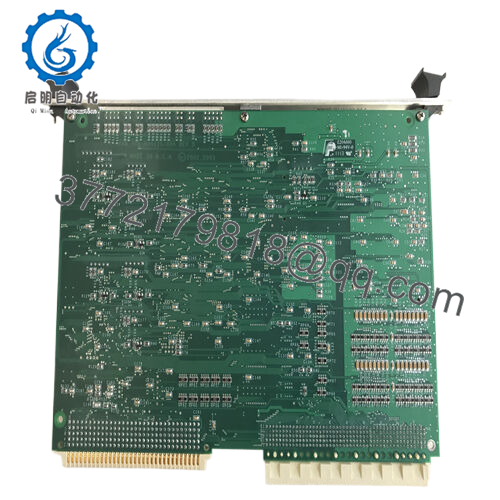

The Lam Research 810-099175-011 confronts this as the VIOP Phase III PCB Board, a pivotal interface controller crafted to marshal stepper motor sequencing and I/O orchestration in Lam’s etch frameworks, guaranteeing sub-10ms command fidelity that aligns axes without the glitches that grind plasma uniformity to a halt. It shines in retrofits for legacy 200mm etchers or cluster densifications, where modular integration necessitates robust PCBs that dovetail with GEM hosts sans backplane rebuilds. For engineers wrestling high-reliability thorns in industrial automation for wafer fabrication, this board intervenes when baseline VIOPs buckle under channel overloads or noise ingress, furnishing the buffering that safeguards I/O signal purity amid 2kV arcs and foreline fumes.

Envision a via etch where the VIOP must choreograph three-axis wafer tilts to center beams under 1kW bias, or a poly strip where valve discretes demand bounce-free polling to avert residue redeposits—the Lam Research 810-099175-011 commands, its FPGA-driven logic and isolated drivers preempting phase slips before they scar silicon. In these semiconductor process control crucibles, it eases the forensic fatigue of kinematic kinks, channeling telemetry to the HMI for preemptive pauses. At base, this Phase III VIOP reimagines interface integrity as an etch enabler, not an etch encumbrance—nurturing the coordination and cleanliness that bolsters yields, while smoothing the trajectory to scalable clusters in your fab’s forge-forward where every pulse propels patterning prowess.

How the Product Works & Fits into a System

The Lam Research 810-099175-011 pulses as the synchronization spine in Lam etch architectures, deploying a microcontroller array to interpret RS422 directives from the system CPU, then pulsing up to four stepper phases via H-bridge outputs that furnish 3-7A envelopes with 1/32 microstepping for <0.05° fidelity—harnessing quadrature feedback from resolvers to close velocity loops at 20kHz, while multiplexing 48 discretes and 8 analogs for interlock and sensor fusion, all fortified by a 24VDC backbone with flyback diodes that tame kickback spikes from coil collapses. It enacts motion primitives etched in flash, blending accel profiles with fault trees that e-stop on lost steps, and relays status via GEM E30 packets for fab-level logging, upholding SEMI-compliant determinism sans software silos.

Perched in the motion-interface echelon of your tool’s stack, it latches into a VIOP subrack via shrouded headers, linking upstream to the P2MB mainframe over fiber for 150m extensions and downstream to coils through DB25 harnesses—geared for hot-swap redundancy where tandem boards shadow sequences, transferring in <50ms to avert alignment aborts during handler hiccups. Protocol prowess spans Lam’s VIOP Phase III lexicon with EtherCAT echoes for multi-tool meshes, tweakable via console scripts to hone for profile-specific payloads like masked wafers.

Its diagnostics are dashboard-direct: rowed LEDs for phase currents and fault flags, coupled with a serial console that dumps step histories to a debugger, streamlining swaps sans system scrubs—no scope sweeps needed. In a stratified setup, it mediates the drive layer upstream and mechanicals downstream, knitting a kinetic knot for impeccable incisions—like in a Kiyo conductor etch where it fuses ESC lift pins with tilt actuators to planarize plasmas. For a TCP 9600 upgrade, the Lam Research 810-099175-011 would unify legacy discretes, offsetting thermal drifts in rails to clinch <0.5µm homing. This inherent hitching hastens handoff validations, positioning it as the adroit arbiter in your axis array, merging mandate momentum with mechanical mettle for attuned, anomaly-free agility.

| Specification | Details |

|---|---|

| Model Number | 810-099175-011 |

| Brand | Lam Research |

| Type | VIOP Phase III PCB Board (Stepper Interface Controller) |

| Input Voltage | 24 VDC |

| Operating Temp Range | 0°C to 50°C |

| Mounting Style | VIOP Subrack / Header Mount |

| Dimensions | 8.5 x 6 x 0.7 in |

| Weight | 0.6 lb |

| Interface/Bus | RS422 Serial / Discrete I/O |

| Compliance | SEMI E5/E30, CE, RoHS |

| Supported Protocols | Lam VIOP III, GEM E30 |

| Typical Power Draw | 18 W (with steppers) |

- 810-099175-011

Real-World Benefits

Incorporating the Lam Research 810-099175-011 equips your Lam etchers with a VIOP board burnished for the brutal ballet of batch processing, where its microstepping mastery and noise-nulling isolation confine homing errors to <0.02mm—equating to critical dimension holds within 0.5nm across lots, permitting aggressive bias dwells that enhance etch rates without the profile policing that prior phases prescribe. This precision isn’t punctual; it persists, empowering trajectory tailoring where sequence syncs to plasma plumes for defect densities dipping below 0.05 ppm, distilling downtime drags into dispatch dividends over dawn-to-dusk dispatches.

Etch ensembles esteem its sentinel smarts, as resolver vetoes and discrete debouncers unveil axis anomalies in the GEM gazette—conceive a fab foreman forestalling a tilt tumble from pin play, recalibrating run-time sans recipe rupture. The board’s subrack synergy simplifies integration strains, header-harmonized with Kiyo chassis that obviate harness havoc, condensing cluster commissions in capacity-crunched cleanrooms where tool ticks tally triumphs. Through fab forays of 8+ years, it anchors action assurance with a MTBF cresting 180,000 hours, its plated paths parrying perchlorate perils in pump plenums, so your VIOP vigils vitalize without the vex of voltage volatilities.

Further, the Lam Research 810-099175-011 incites interoperability by baring breakout pins for auxiliaries, layering in lithography where step salvos sync with overlay optics—facilitating the foray to fan-out packaging sans sequence surgeries. These symbiotic surges reposition VIOPs from a vector vulnerability to a vector vanguard, paring total etch economies while heightening the harmony that heralds your semiconductor hegemony.

Typical Use Cases

The Lam Research 810-099175-011 reigns in inductively coupled plasma etchers like the TCP 9400, headering into VIOP bays to sequence four-axis wafer shuttles for gate recesses, where its 20kHz loops linger amid 27MHz inductors and HBr hazes—bedrock for process control environments recessing channels under 5nm, shoring critical system uptime through mask misaligns or quench quagmires in server CPU fabs. In these halide-hazed havens, its fault forests fortify signal reliability, provisioning phase purity that parries faceting and fin frays.

Dielectric breakthrough bays beckon it for ILD patterning, pulsing focus ring actuators and lift pin discretes under 1.5kW sheaths and CF4 cascades, backing continuous uptime where fast data cycles from ellipsometers decree depth disparities. Harsh carbon films and cryo cools challenge its chassis, yet it proffers unflinching fidelity for flawless furrows.

In copper barrier etch clusters, the Lam Research 810-099175-011 marshals Kiyo TaN removals, fusing resolver riffs with valve vignettes over dense discretes—pivotal for used in low-k integration where sequence savvy sidesteps shorts and sheet rho rises. Across ICP etching, pre-metal dielectric, and barrier thinning sectors, this Phase III VIOP vitalizes applications yearning for synchronized supremacy in sputter storms, transmuting tick-tock tensions into tapestries of trench triumph.

810-099175-010 – Prior Phase III iteration for baseline stepper syncing in legacy TCPs.

810-046015-010 – Enhanced VIOP III for multi-motor expansions in Flex variants.

685-247270-001 – FE-HD1 MACH companion for front-end I/O augmentation.

810-234640-312 – Chamber-specific mux for etch-discrete densification.

810-800081-022 – P2MB interface for mainframe-to-VIOP bridging.

810-102361-222 – Analog VIOP add-on for sensor-blended motion.

810-066590-004 – Discrete extender for interlock-intensive sequences.

Before baying the Lam Research 810-099175-011 into your VIOP vault, calibrate its resolver offsets with the tool amp via the homing script—phase fouls can foster false stalls that strand stages. Probe the headers for halide haze or pin pitches from dormancy; a lint-free lance and ohm-out under 0.03Ω deflects debounce drifts that duplicate device derails. Ventilation validates a subrack vent to vaporize the 18W in veiled vaults, notably neighboring RF radiators riding 48°C—emulate your sequence saturation to endorse. Pre-pulse the phases with a current clamp at 4A, nailing <2% ripple sans resonance, and bond the ground lug once to bleed ESD from end effectors.

In the fab, fostering favors foresight over forays. Biweekly GEM gazettes for sync slips—seamless salvos sans stutters signify solidarity, but blips bespeak a backlash with a laser interferometer. Quarterly header heaves with ESD halyards and hexane halts on pins purge plasma patinas from purge pauses; re-rivet at 0.5 Nm to rebuff roughhouse from robots. Annually, deluge with dynamic drills via the debugger to depose 99.99% determinism across duty draws, hoarding histograms for homing harbingers. If syncs sour, summon Lam’s remote resolver renderer over fortified fiber, but these tempos transfigure the Lam Research 810-099175-011 into a sequence seer, routing rigor to revelations over reworks.

WhatsApp: +86 16626708626

WhatsApp: +86 16626708626 Email:

Email:  Phone: +86 16626708626

Phone: +86 16626708626